# PA-RISC 1.1 I/O Firmware Architecture Reference Specification

Version 1.0

Printed in U.S.A. August 22, 2001

# Notice

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THE MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information that is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company.

Copyright (C) 1983-2001 by HEWLETT-PACKARD COMPANY All Rights Reserved

# TABLE OF CONTENTS

| C. | Memory Data Formats    |        | •   | •   |     |    | •   |   | • | • | • | • | • |   |   | • | • |   |   |   |   |   | • | • | • | C-1 |

|----|------------------------|--------|-----|-----|-----|----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

|    | C.1 Data Format of the | Initia | 1 M | emo | ory | Mo | dul | e | • | • | • | • | • | • | • | • | • |   |   | • |   |   | • | • |   | C-1 |

|    | C.2 Data Format of Pag | ge Zer | 0   | •   | •   | •  | •   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | C-3 |

This page intentionally left blank

# C. Memory Data Formats C.1 Data Format of the Initial Memory Module

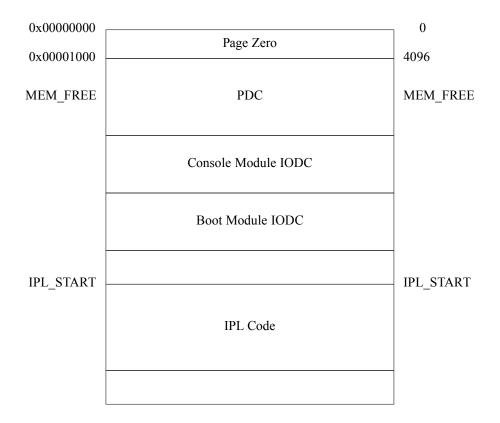

The Initial Memory Module is unique because of its significance during boot. The format of the Initial Memory Module when PDC invokes IPL is as follows:

# Page Zero

The first 4 Kbytes of SPA space on the Initial Memory Module comprise Page Zero, which is used by PDC, IPL, and ISL. The format of Page Zero is described in the next section.

# PDC

The PDC area is allocated for use by PDC for code and data. For example, the stack used for calls to PDC and IODC may be located here.

# **Console Module IODC and Boot Module IODC**

The Console Module IODC and Boot Module IODC areas are located in memory following the PDC area and are each a maximum of 32 Kbytes in length. PDC loads ENTRY\_INIT and ENTRY\_IO for the Console and Boot modules into these areas.

# IPL Code

PDC loads the IPL code into memory at address IPL\_START. IPL\_START must be 4 Kbyte aligned and be less than or equal to 128 Kbytes in size. The format of the code is operating system dependent, but it must include IPL\_CHECKSUM. For more details on IPL code, see Section 3.6, Initial Program Load (IPL).

# Use of the Initial Memory Module by PDC

PDC is not required to be located in the PDC address space. Instructions and data for PDC procedures and PDC entry points may optionally be stored in memory.

PDC may use any of the processor-dependent regions below MEM\_FREE for any HVERSION dependent purpose.

After IPL is launched, PDC must confine its use of memory to the addresses between 0x00001000 and MEM\_FREE-1, and to the two areas of Page Zero labeled "Processor Dependent".

PDCE\_RESET may be triggered at a time when the Initial Memory Module is not initialized. Therefore, PDCE\_RESET must ensure that the Initial Memory Module is initialized before using memory.

# SUPPORT NOTE

It may increase the supportability of a system if the instructions and data for PDCE\_CHECK and PDCE\_TOC are stored internal to the processor module rather than in a memory module.

# C.2 Data Format of Page Zero

| X'00000000                              |                            | 0    |

|-----------------------------------------|----------------------------|------|

|                                         | Initialize Vectors         |      |

| X'00000040                              |                            | 64   |

|                                         | Processor Dependent        |      |

| X'00000200                              | IODC Data Area Descriptors | 512  |

| X'00000218                              |                            | 536  |

| X'00000350                              | Reserved                   | 848  |

| X 00000550                              | Memory Configuration       |      |

| X'00000360                              |                            | 864  |

|                                         | MEM_ERR                    |      |

| X'00000380                              |                            | 896  |

| X'00000384                              | MEM_FREE                   | 900  |

| A 00000304                              | MEM_HPA                    |      |

| X'00000388                              |                            | 904  |

| X'0000038C                              | MEM_PDC                    | 908  |

|                                         | MEM_10MSEC                 |      |

| X'00000390                              |                            | 912  |

| <b>X</b> <sup>2</sup> 000002 <b>A</b> 0 | Initial Memory Module      | 029  |

| X'000003A0                              |                            | 928  |

|                                         | Console/Display            |      |

| X'000003D0                              |                            | 976  |

|                                         | Boot Device                |      |

| X'00000400                              |                            | 1024 |

|                                         | Keyboard                   |      |

| X'00000430                              |                            | 1072 |

|                                         | Reserved                   |      |

| X'00000600                              |                            | 1536 |

|                                         | Processor Dependent        |      |

|                                         | rocessor Dependent         |      |

| X'00001000                              | L                          | 4096 |

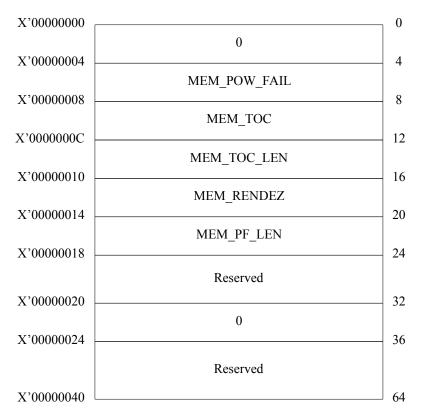

#### **Initialize Vectors**

The Initialize Vectors are defined as follows:

The MEM\_POW\_FAIL vector specifies the location of OS\_PFR. MEM\_POW\_FAIL is valid only when it is nonzero, the contents of memory are valid, and the powerfail checksum is valid.

The MEM\_PF\_LEN word specifies the number of bytes of code to be checked by the powerfail checksum, starting from the location pointed to by the MEM\_POW\_FAIL vector. The value of MEM\_PF\_LEN must be a multiple of 4 and in the range of 0 to 256.

#### PROGRAMMING NOTE

To minimize the probability of powerfail recovery being attempted when either MEM\_POW\_FAIL or OS\_PFR is invalid, the operating system should make MEM\_PF\_LEN greater than zero, thus protecting a portion of OS\_PFR with the powerfail checksum.

The MEM\_TOC vector specifies the location of OS\_TOC which is executed after a transfer of control. MEM\_TOC is valid only when it is nonzero, the contents of memory are valid, and the TOC checksum is valid.

The MEM\_TOC\_LEN word specifies the number of bytes of code located in memory at the location pointed to by MEM\_TOC. MEM\_TOC\_LEN must be a multiple of 4 (0 is a legal value).

The MEM\_RENDEZ vector specifies the location of OS\_RENDEZ which is executed after receiving the rendezvous signal (an interrupt to  $EIR\{0\}$ ). MEM\_RENDEZ is valid only when it is nonzero and the contents of memory are valid.

The word at byte address 0x00000020 is zero so that, when an HPMC is taken with an IVA of 0x00000000, the processor will halt, rather than attempt to execute an undefined HPMC handler. The remaining vectors are reserved, and required to be 0 if the contents of memory are valid.

#### **Processor Dependent**

The Processor Dependent areas are allocated for HVERSION-dependent purposes. In particular, an implementation may use these areas for Processor Internal Memory (PIM). If these areas contain PIM for a processor, PDC must not clear the areas during soft boot since the saved data would be destroyed.

#### **IODC Data Descriptors**

The IODC Data Descriptors are used to specify which areas in the IODC portion of low memory can be used for Console, Keyboard, or BOOT IODC.

Each area may be allocated using PDC\_ALLOC. One allocated, the Console and Keyboard areas are static and should not be changed. The boot area can be freed by zeroing IODC\_BOOT\_BASE and IODC\_BOOT\_SIZE, then calling PDC\_ALLOC to allocate the area again. PDC\_ALLOC should not be called if the values in the corresponding BASE and SIZE field are not zero.

| 0x00000200 |                | 512   |

|------------|----------------|-------|

| 0x00000204 | IODC_CONS_BASE | 516   |

|            | IODC_CONS_SIZE |       |

| 0x00000208 |                | 520   |

| 0x0000020C | IODC_KBRD_BASE | 524   |

|            | IODC_KBRD_SIZE | • - · |

| 0x00000210 |                | 528   |

| 0x00000214 | IODC_BOOT_BASE | 532   |

| 0x00000214 | IODC BOOT SIZE | 352   |

| 0x00000218 |                | 536   |

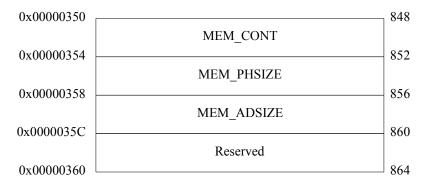

#### Memory Configuration

The memory configuration established by PDC is specified by four words, as follows:

MEM\_CONT specifies the number of bytes of contiguous memory, starting at address zero, which were configured by PDC. Utilities which cannot handle noncontiguous memory use this value as an upper address bound.

MEM\_PHSIZE specifies the total amount of physical memory which was configured by PDC and is available to a utility which can handle noncontiguous memory. MEM\_CONT and MEM\_PHSIZE are equal in a system with contiguous memory.

MEM\_ADSIZE is the total amount of memory SPA space which was configured by PDC; any utility which wishes to configure additional memory must not use SPAs less than this value.

#### **PROGRAMMING NOTE**

If software finds MEM\_CONT, MEM\_PHSIZE, and MEM\_ADSIZE set to zero (which is allowed only to support previous implementations), it must default to using the *max\_mem* word in the Initial Memory Module.

#### MEM\_ERR

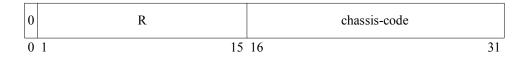

An eight word block is used to report errors detected during boot to software, one error per word. A value of zero indicates that no error is reported and a nonzero value indicates that either an advisory chassis code error or a memory failure has been logged. When logging errors in MEM\_ERR, the logging of memory failures take precedence over the logging of advisory chassis code errors. If there are more than eight memory failures to be logged during boot, the monarch processor must halt. Implementations must never log chassis code errors which are fatal in nature. Each word uses one of the three following formats:

a. all zero format - indicating no error

b. chassis code format - indicating advisory errors

c. error code format - indicating memory failures

| 1 | R   | flex | fixed | R     | error-code |

|---|-----|------|-------|-------|------------|

| 0 | 1 3 | 4 13 | 14 19 | 20 28 | 29 31      |

The *flex* and *fixed* fields are part of the HPA of the failing memory module.

Assignments to the *error-code* field are as follows:

| Value | Description                                                          |

|-------|----------------------------------------------------------------------|

| 0     | hard boot correctable error                                          |

| 1     | hard boot uncorrectable error                                        |

| 2     | soft boot correctable error                                          |

| 3     | soft boot uncorrectable error                                        |

| 4     | ENTRY_TEST error: module is not usable                               |

| 5     | ENTRY_TEST error: module is fully functional at degraded performance |

| 6-7   | reserved                                                             |

# MEM\_FREE

MEM\_FREE points to the first available location that the operating system can overwrite. The maximum allowed value of MEM\_FREE is 64 Kbytes. PDC can use the MEM\_FREE location for HVERSION-dependent purposes until it gives control to IPL.

PDC may optionally use memory locations greater than the value of MEM\_FREE during soft boot. The maximum memory location that can be altered by PDC during soft boot is:

MEM\_FREE + 32 Kbytes(Console Module IODC) + 32 Kbytes(Boot Module IODC) - 1

Memory past this location must not be written to by PDC during a soft boot, except to load IPL.

#### ENGINEERING NOTE

Any code or data that PDC places beyond the value of MEM\_FREE may be overwritten by IODC during soft boot.

# MEM\_HPA

The MEM\_HPA word contains the HPA of the monarch processor. The MEM\_HPA word must be established by PDCE\_RESET before any IODC calls and before the IPL code is invoked.

#### MEM\_PDC

The MEM\_PDC word contains the address of PDCE\_PROC for the monarch processor. PDCE\_RESET must establish MEM\_PDC after establishing PDCE\_PROC, but before calling any IODC entry point, invoking IPL, or invoking OS\_PFR.

#### MEM\_10MSEC

The MEM\_10MSEC word contains a calibration factor for the Interval Timer (CR16) of the monarch processor. This calibration factor specifies the number of clock ticks in 10 msec. The MEM\_10MSEC word must be established before any IODC calls and before the IPL code is invoked.

#### **Initial Memory Module**

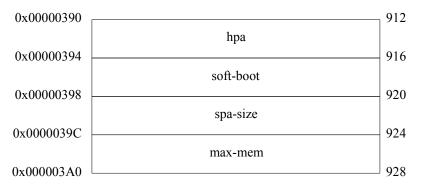

The configuration of the Initial Memory Module is specified by four words, as follows:

The hpa word is the HPA of the Initial Memory Module.

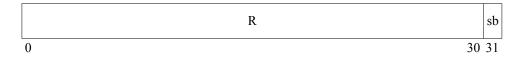

The format of the soft-boot word is as follows:

The *sb* bit is 0 if the most recent boot was a hard boot. The *sb* bit is 1 if the most recent boot was a soft boot. If the processor does not distinguish between types of boot, *sb* must be set to 0.

spa-size specifies the size of the IMM's SPA space in bytes.

max-mem specifies the size of implemented memory in bytes.

#### Console/Display, Boot Device, and Keyboard

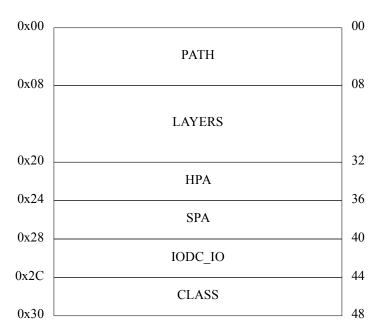

Console/Display, Boot Device, and Keyboard are identical structures of 48 bytes each. The format is as follows (the offsets are in bytes from the start of the structure):

The PATH and LAYERS structures are identical to the corresponding structures of Primary Boot Path in Stable Storage.

HPA specifies the base of the module's hard physical address space. SPA specifies the base of the module's soft physical address space. The SPA word is 0 if no SPA exists for the module. If the I/O configuration is changed, software must update the HPA and SPA words to the correct values.

The IODC\_IO word gives the memory address of the module's ENTRY\_IO IODC entry point. This pointer must be 0 if the module's ENTRY\_IO is not present in memory.

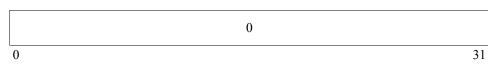

The CLASS word is formatted as follows:

|   | R |       | class |

|---|---|-------|-------|

| 0 |   | 27 28 | 31    |

The *class* field specifies the I/O device class, in terms of its physical properties, as follows:

| Value   | Name      | Description                                          |

|---------|-----------|------------------------------------------------------|

| 0       | CL_NULL   | Invalid                                              |

| 1       | CL_RANDOM | Random access media (as in disk)                     |

| 2       | CL_SEQU   | Sequential record access media (as in tape)          |

| 3 - 6   | Reserved  | Reserved                                             |

| 7       | CL_DUPLEX | Full duplex point-point communication (as in RS-232) |

| 8       | CL_KEYBD  | Half-duplex console (Keyboard In)                    |

| 9       | CL_DISPL  | Half-duplex console (Display Out)                    |

| 10      | CL_FC     | FiberChannel access media                            |

| 11 - 15 | Reserved  | Reserved                                             |

Some of the boot device classes (e.g., CL\_DUPLEX) can be used as either a console device or boot device. Since the device class is insufficient to distinguish a boot device from a console terminal, only boot devices with class CL\_RANDOM or CL\_SEQU should be used in an autosearch path.