# JOURNAL

AUGUST 1986

© Copr. 1949-1998 Hewlett-Packard Co.

# JOURNAL

#### Articles

**4** Hewlett-Packard Precision Architecture: The Processor, by Michael J. Mahon, Ruby Bei-Loh Lee, Terrence C. Miller, Jerome C. Huck, and William R. Bryg. Here is the RISClike architecture that will govern the design of HP computers for at least the next decade.

8 Floating-Point Coprocessor 16 HP Precision Architecture Caches and TLBs

23 Hewlett-Packard Precision Architecture: The Input/Output System, by David V. James, Stephen G. Burger, and Robert D. Odineal It achieves goals of scalability, leverageability, and flexibility.

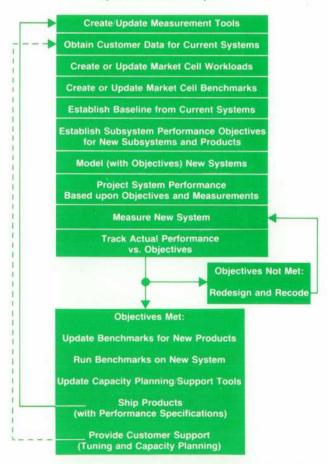

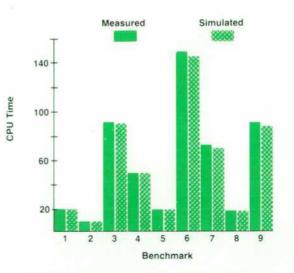

**30** Hewlett-Packard Precision Architecture Performance Analysis, by Joseph A. Lukes How did performance analysis influence the architecture? What methods were used?

**40** The HP Precision Simulator, by Daniel J. Magenheimer In its early days, it had to accommodate frequent instruction-set changes and give timely feedback to the architecture designers.

43 Remote Debugger

#### Departments

- 3 In this Issue

- 3 What's Ahead

- 21 Authors

- 44 Reader Forum

Editor, Richard P. Dolan

Associate Editor, Business Manager, Kenneth A. Shaw

Assistant Editor, Nancy R. Teater

Art Director, Photographer, Arvid A. Danielson

Support Supervisor, Susan E. Wright

Illustrator, Nancy Contreras

Administrative Services, Typography, Anne S. LoPresti

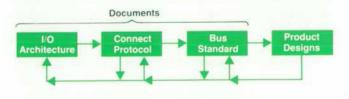

European Production Supervisor, Michael Zandwijken

#### In this Issue

The HP Precision Architecture development program, known within HP as the Spectrum program, is the largest system development program ever undertaken by the Hewlett-Packard Company. The program developed not only a new system architecture, but also all hardware and software components necessary to constitute an entirely new computer system family. It encompassed architecture, VLSI technology, the MPE XL commercial operating system, the HP-UX real-time standard UNIX operating system, a new family of optimizing compilers, a new data base facility, and integration with the HP AdvanceNet networking strategy.

The papers published in the August 1985 and January 1986 issues of the HP Journal outline the reasons for the development of HP Precision Architecture and describe the structure of the next generation compiler family. In this issue of the HP Journal, we are happy to be able to present the first of a planned set of papers that explain key program elements in greater levels of detail. We intend these papers to be tutorial in nature, describing and explaining program elements and presenting the basic research and measurement results that were achieved.

In this issue we begin with papers covering an overview of the processor architecture (page 4), a summary of the I/O architecture (page 23), a description of the performance analysis activities used throughout the program (page 30), and a description of the simulator tools that grew into our general software diagnostic tools (page 40). In subsequent issues, we plan to present papers describing hardware components, software system components, software engineering practices, and performance results. We expect that the collected set of papers will then constitute a good technical overview of the Spectrum program and the key research results that emerged from it.

-William S. Worley, Jr. Guest Editor

#### Cover

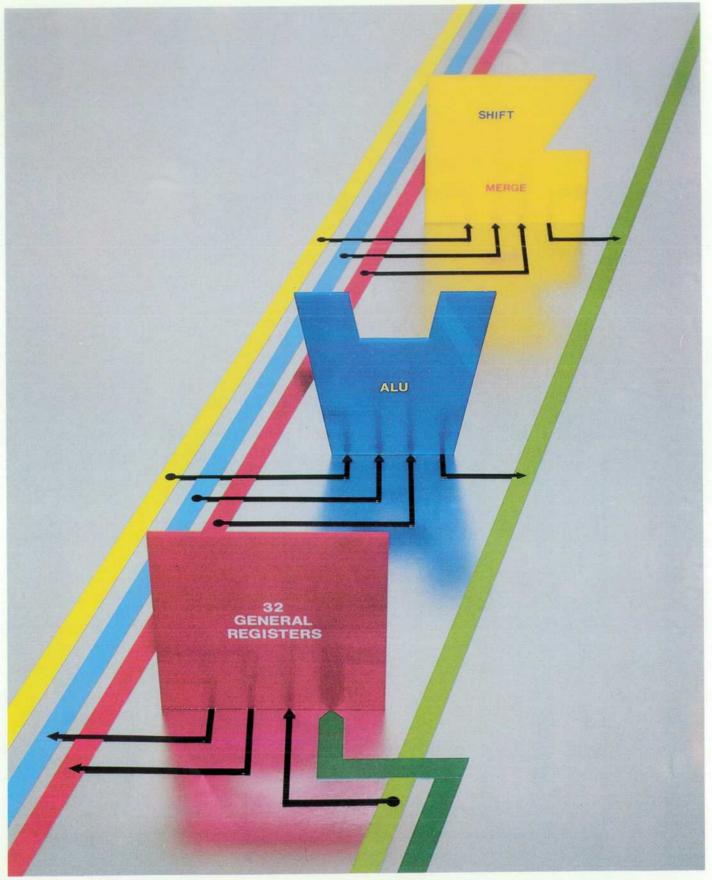

The cover photograph shows a "block diagram" representing the HP Precision Architecture execution engine, which is shown more conventionally in Fig. 3 on page 7.

#### What's Ahead

Next month's issue will have a series of articles on the design of the HP 9000 Series 300 modular engineering workstations, and a part historical, part tutorial treatise on implementing a worldwide electronic mail system, based on HP's experience with its own HP DeskManager product.

The HP Journal encourages technical discussion of the topics presented in recent articles and will publish letters expected to be of interest to our readers. Letters must be brief and are subject to editing. Letters should be addressed to: Editor, Hewlett-Packard Journal, 3000 Hanover Street, Palo Alto, CA 94304, U.S.A.

## Hewlett-Packard Precision Architecture: The Processor

This article describes the architecture's basic organization, execution model, control flow model, addressing and protection model, functional operations, and instruction formats and encoding.

#### by Michael J. Mahon, Ruby Bei-Loh Lee, Terrence C. Miller, Jerome C. Huck, and William R. Bryg

"Everything should be made as simple as possible, but not simpler." Albert Einstein

HE HP PRECISION ARCHITECTURE development program had the objective of designing a computer architecture capable enough and versatile enough to excel in all of Hewlett Packard's computer markets: commercial, engineering and scientific, and manufacturing. Such an architecture would have to scale easily across a broad performance range, provide for straightforward migration of applications from existing systems, and serve as the architectural foundation for at least the next decade of product development.

To address this problem, an unusual group of people was brought together, from within and outside Hewlett-Packard, possessing unusually diverse experience and training. Under the leadership of Bill Worley, this small group of compiler designers, operating system designers, performance analysts, hardware designers, microcoders, and system architects was forged into a team. The intent was to bring together many different perspectives, so that the team could deal effectively with design trade-offs that cross the traditional boundaries between disciplines.

The design methodology was as unusual as the team. It was an iterative, closed-loop, measurement-oriented approach to computer architecture. The process began with data collection and analysis of what computers—Hewlett-Packard's and others'—were actually doing during application execution. Early results validated the suggestions of some RISC architecture researchers that simpler designs were a better match to the actual behavior of machines, and could substantially improve cost/performance.<sup>1</sup> The scalability and generality requirements provided further incentives to reduce system complexity.

After a simple "core" architecture was postulated, the team examined it intensively through simulation and measurement. We evaluated its suitability as a target for compilation and optimization, and as a host for modern operating systems. Logic designs were done simultaneously in several circuit and packaging technologies to evaluate the implications of the architectural decisions on hardware realizations.

After a round of evaluation, the results became the basis for a series of proposed refinements to the architecture. After critical study, the best proposals were incorporated into the architecture, the simulator was updated, and the evaluation process began again.

This process continued for four major (and many minor) iterations over a period of 18 months. At each successive iteration, the architecture and all proposed changes were published internally for review by key technical people in product divisions. As the project progressed, an increasing proportion of the proposals and evaluations came from divisional participants.

The iterative design sometimes resulted in adding a function. For example, the frequent requirement to shift index registers to index to half words, words, or double words in a byte-addressed machine led to the addition of a zero-tothree-bit preshifter to scale one of the inputs to the adder.

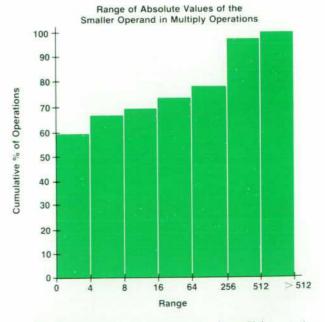

More frequently, iteration resulted in deleting mechanisms revealed as too onerous or too little used. An example is the deletion of the STORE INDEXED instruction, because it was the only instruction that would have required a register file capable of reading three registers simultaneously. Compiler strategies were found that all but eliminated the need for the STORE INDEXED instruction, which in any case could be simulated in two instructions. Another example was the deletion of a rather irregular MULTIPLY STEP instruction, when it was discovered that virtually all integer multiplications could be performed efficiently using SHIFT AND ADD instructions, which were a natural byproduct of the index preshifter described above.

The result of this process is an architecture honed by data, tested against various implementation technologies, and broadly tuned to a wide variety of system and application tasks.

#### **Overview**

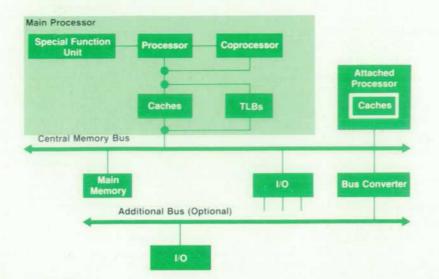

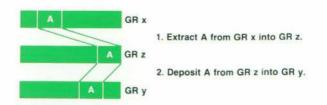

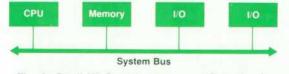

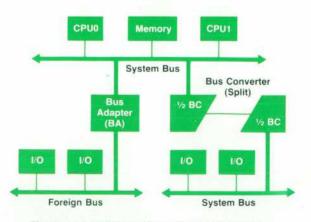

An HP Precision processor is one element of a complete system. The system also includes memory arrays, I/O devices, attached processors, and interconnection structures such as buses and networks. Fig. 1 shows a typical system. The processor interfaces to a central bus like any other module and uses the bus to reference main memory and I/O devices. External interrupts are also transmitted over the buses.

#### Fig. 1. HP Precision Architecture system organization.

#### **Processor Overview**

The processor module is organized as instruction fetch and execute units with a tightly coupled high-speed cache system. While a cache is optional, it is such a cost-effective component that nearly all processors will incorporate this hardware. The processor module may also include a hardware address translation table called a *translation lookaside buffer* or *TLB*, and *assist hardware* for extra functions such as floating-point operations. The main data paths are 32 bits wide, and the memory system is byte addressed.

The execution unit performs data transformations on local registers and generates addresses to reference the cache and main memory. It has a memory system interface for moving data operands between the memory system and the registers. The execution unit may be supplemented by assist hardware—coprocessors or special function units to augment its capabilities for application-specific operations or data types. This is discussed further in the sections on the execution model.

The fetch unit calculates the instruction address, fetches the instruction, decodes it, and sends information to the execution unit. The fetch unit greatly benefits from a reduced-complexity instruction set. Instructions are all fixedwidth 32-bit objects, simplifying decoding and calculation of the next instruction address. The fetch unit is responsible for the control flow in the processing of instructions. This is discussed further in later sections on the control model.

HP Precision Architecture uses a memory hierarchy as a cost-effective means of achieving nearly the speed of the fastest (highest) memory level, with the capacity of the largest (lowest) memory level. The highest level of the hierarchy is the registers, followed by the caches. Main memory is the next level and the I/O system provides the largest and slowest level of storage. In HP Precision Architecture, the cache system is architecturally visible in the sense that there are cache control instructions for cache management. A virtual memory system is a characteristic feature on all but the smallest HP Precision processors. Virtual address protection and translation provide security and a large, flat, global address space for all processes. This is discussed further in the sections on the addressing and protection model. Provisions are made for attached processors, which interface to the system hierarchy at the memory bus level, and typically have their own registers and local cache system. Attached processors can provide such functions as I/O or vector processing. Clustered and tightly coupled multiprocessing are also supported for modular expansion of the system.

#### **Processing Resources**

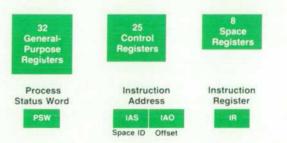

The processing resources are organized around three register arrays and a few specialized registers (see Fig. 2). The general register array contains general-purpose registers used for all computations. The space register array is used to build virtual addresses. The control register array is a collection of registers used for virtual address protection, interruption processing, and other miscellaneous functions.

The general register array contains thirty-two 32-bit general-purpose registers. Register zero is special: it always returns zero when read and discards any result when used as a target register. This specialization is easily implemented in hardware and eliminates the need for instructions for unary or condition-testing operations. For example, a copy operation is a logical OR with register zero and unary SUB-TRACT also uses register zero as a source. Registers 1 and 31 are also specialized as implied targets for a few instructions that have no space in the instruction for target register specifiers.

The space register array contains eight registers. When

Fig. 2. HP Precision Architecture processing resources are organized around three register arrays and a few specialized registers.

one of these is concatenated to a 32-bit address offset, a virtual address is formed. Three levels of the architecture are defined, according to the amount and degree of virtual addressing supported. The level-zero HP Precision processor does not support any virtual addressing and need not implement the space registers. When building a processor for a highly integrated, dedicated system, it is a considerable savings in hardware cost to eliminate the virtual address hardware. General-purpose computers, however, require virtual addressing. A level-one processor supports 16-bit space registers for a 48-bit virtual address space and a level-two processor implements 32-bit space registers to allow the full 64-bit virtual address space.

The control register array consists of twenty-five registers which contain system state information. Four of these control registers are used by the virtual address system to identify protection groups for the current process. The shift amount for instructions that perform variable-length shifts is stored in a control register. An interval timer is included as a control register. The configuration of coprocessors in a system is also stored in a control register. The remaining control registers are used as temporary registers and to record the state of the machine at the time of an interruption.

An HP Precision processor also maintains registers for the current instruction address, the current instruction, and the processor status word (PSW). The current instruction address is divided into its virtual space identifier (IAS) and its offset (IAO) within the space. The instruction register (IR) contains the current instruction. The PSW holds various flags for enabling virtual addressing, protection, interruptions, and other status information.

Fig. 2 shows the processing resources. A complete context switch only involves the saving of the general registers, the space registers, and several of the control registers. The instruction address registers and PSW are saved in control registers by the hardware at the time of any interruption. Since the process state is small and no extra manipulation of cache or TLB (translation lookaside buffer) structures is necessary, fast context switching is obtained. No additional resources are needed to save intermediate machine states, since interruptions are always taken at instruction boundaries.

#### Data Types

HP Precision Architecture supports data types for arithmetic, logical, and field manipulation operations. All data objects must be stored on their naturally aligned addresses, that is, 32-bit data objects must start on word-aligned (fourbyte) addresses, 16-bit data objects must start on half-wordaligned addresses, and 8-bit data objects must start on bytealigned addresses. This general alignment rule is easily obeyed by software and significantly improves the cost and speed of cache memory hardware. It also eliminates the possibility of a cache miss or address translation fault in the middle of a data or instruction reference, thereby simplifying the processor control.

Signed and unsigned integers may be 8, 16, or 32 bits long. Signed integers are represented in two's complement form. Characters are 8 bits long and conform to the ASCII standard. While bits are not directly addressable, efficient support is provided to manipulate and test individual bits and bit fields in general registers. Both packed and unpacked representations of decimal numbers are supported by software. Packed data is always aligned on a word boundary and consists of 7, 15, 23, or 31 BCD digits, followed by a sign digit.

Floating-point numbers are addressed as 32-bit (singleprecision) or 64-bit (double-precision) quantities. The coprocessor interface allows this wider data path for loading and storing double-precision floating-point operands. The floating-point data format conforms to the ANSI/IEEE 754-1985 standard.

#### **Execution Model**

HP Precision Architecture assumes a register-based execution model, with all operands coming from registers and all results going back into registers. The thirty-two general-purpose registers are used for local storage of operands, intermediate results, and addresses.

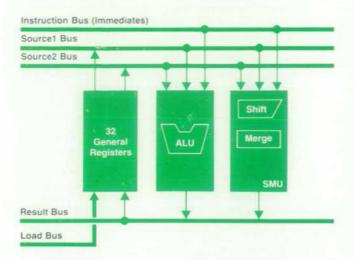

The execution engine for the basic HP Precision instruction set consists of a simple arithmetic logic unit (ALU) and a shift-merge unit (SMU), as shown in Fig. 3. The ALU has a preshifter on one port and a complementer on the other port. The SMU consists of a shifter and a mask-merger. It is used for implementing field manipulation operations. The shifter concatenates two 32-bit operands and performs a right shift. The mask-merger selects a contiguous field of bits from the output of the shifter and merges this with the other bits from its second input source, forming a 32-bit result. The second input source to the mask-merger may be a mask of all zeros or all sign bits, or may come from a general register.

The typical execution data flow consists of reading two operands from general-purpose registers, routing these two operands through the ALU or the SMU with the proper function selected, and storing the result back into a general register. This is the data flow for the basic three-register model of execution, which facilitates single-cycle execution, since no memory references are required.

#### Single-Cycle Execution

A primary design goal was that all functional computations in the basic instruction set could execute in one machine cycle in a pipelined implementation of the processor architecture. Operations were selected for inclusion in the basic instruction set only if they could be implemented in a reasonably small number of logic levels, to guarantee a short cycle time. This does not necessarily mean that the operation performed had to be primitive in function. In fact, rather sophisticated operations were allowed in the architecture if they proved useful to the compilers, and were implementable in a short machine cycle with relatively simple hardware.

.

Complex operations that are necessary to support required software functions but cannot be implemented in a single execution cycle are broken down into primitive operations, each of which can be executed in a single cycle. Examples are the DECIMAL CORRECT operations which are primitive operations for performing arithmetic on BCD data, the SHIFT AND ADD operations which are primitives

Fig. 3. The execution data path consists of a simple arithmetic logic unit (ALU) and a shift-merge unit (SMU).

for integer multiplication, and the DIVIDE STEP operation which is a primitive for integer division.

Single-cycle execution was a design goal of the architecture, but is not a constraint on the implementations. For example, an HP Precision microprocessor may operate with slower memories, performing a load instruction in more than one cycle.

#### Immediates

A notable aspect of HP Precision Architecture's registerbased model of execution is its heavy use of the instruction register as a source for operands, in addition to the thirtytwo general-purpose registers. Many HP Precision instructions have an immediate field embedded in the 32-bit fixedlength instruction. These immediates are made maximallength, in the sense that they fill up all unassigned bits in the given instruction. This maximizes the probability that a constant can be represented in the instruction as immediate data. Although immediates come in various sizes in different instruction classes, their sign bit is always in a fixed position. An immediate operand is advantageous since it does not have to be loaded to a general register and therefore saves both a memory access and the use of a general register.

Although maximal-length immediates in an instruction are capable of representing most of the constant values that are needed, it is desirable to have the capability of embedding full-length 32-bit immediates in the instruction stream. HP Precision Architecture does this by means of a pair of instructions. First, a long-immediate instruction is used to load or add the most significant twenty-one bits of the immediate value, padded on the right with eleven zeros, into a general register. A subsequent instruction, using this register as the base register, supplies the low-order bits to complete the 32-bit immediate. In this way, a 32-bit constant value can be placed in a general register, or a load or store instruction can be performed with a full 32-bit static displacement. An alternative approach-creating a doubleword instruction-would have introduced the more complex possibility of a page fault occurring in the middle of an instruction fetch.

#### Load and Store Operations

The general register array is the only level of the memory hierarchy that interacts with the execution engine. The general registers interact with the rest of the memory hierarchy via the LOAD and STORE instructions.

The LOAD and STORE instructions are designed to execute in a single cycle in a pipelined implementation of the architecture that includes a data cache memory that operates at the speed of the processor. This immediately excludes the specification of multiple loads and stores or levels of address indirection in a single instruction.

Even with a fast cache memory, data may not be available until one cycle after the memory access is initiated. Therefore, following a load instruction, the software tries to schedule one or more instructions that do not use the target register being loaded. However, the hardware must be able to interlock the pipe if an instruction following a load instruction uses the target register that has not yet been loaded.

The size of the data item loaded or stored can be a byte, a half word, or a full word. It is possible to store any contiguous sequence of bytes within a word, either starting from the leftmost byte or ending with the rightmost byte, using the STORE BYTES instruction. For example, it is possible to store the leftmost three bytes or the rightmost three bytes of a register into three contiguous bytes of memory. This instruction is a useful primitive for moving unaligned strings of bytes from one memory location to another.

All address calculation in the LOAD and STORE instructions is based on the base register plus displacement addressing mode. The displacement can be a long 14-bit signed displacement, a short 5-bit signed displacement, or an index register. An index register, if used, may optionally be shifted left by 1, 2, or 3 bits to permit integer addressing to half words, words, or double words, respectively. Both the base register and the index register used in address calculation can come from any of the general registers.

Flexible Address Modification Mechanisms. Automatic address modification mechanisms allow one to walk through a data structure more efficiently, by updating the address register to the next item in the data structure to be referenced while fetching the current item.

Flexible address modification mechanisms are included in HP Precision Architecture, providing high-performance functionality in a single cycle. For example, it is possible to modify the base register for a subsequent load or store instruction by adding to it the long or the short displacement value specified in the instruction itself, or the value of an index register, optionally shifted to multiply by the size of the object to be loaded or stored.

If address modification is specified, either premodification or postmodification can be performed. *Premodification* means that the address calculation is performed and the result used as the address to initiate the memory access. *Postmodification* means that the original content of the base register is used as the address to initiate the memory access.

An unusual feature of this premodify or postmodify addressing mode is that in the long-displacement instructions, the sign bit of the displacement is also used as the bit to select premodification or postmodification. This al-

#### **Floating-Point Coprocessor**

HP Precision Architecture generally conforms to the concept of a simple instruction set realizable in cost-effective hardware. However, certain algorithms like floating-point operations realize substantial performance gains when implemented on specialized hardware. The floating-point instruction set is an example of HP Precision Architecture's instruction extension capabilities.

Floating-point instructions are supported through an assist coprocessor to provide high-performance numeric processing. As a coprocessor, the floating-point unit contains its own register file and executes concurrently with the basic processor. Operands from the caches are loaded or stored from any of twelve floating-point registers. The data format, all operations, and exceptions fully conform to the ANSI/IEEE 754-1985 standard. Very high-performance coprocessors can be implemented by combining hardware pipelining with the HP Precision highlevel language optimizer.

The floating-point coprocessor is organized like the basic processor. All operands from main memory are referenced using coprocessor load and store instructions. Normal virtual address translation and protection checks are made and data is transferred between the cache (or memory) and the floating-point register file. Both single-precision (4-byte) and double-precision (8-byte) operands can be referenced with a single instruction. Quad-precision (16-byte) operands are referenced using a pair of double-precision coprocessor memory reference instructions.

The basic processor performs index and short-displacement address calculations for the coprocessor load and store instructions. While STORE INDEXED instructions are not provided for the basic processor, COPROCESSOR STORE INDEXED instructions are provided since only two general register reads and a nonconflicting coprocessor register read are required.

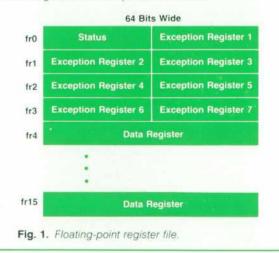

#### Floating-Point Register File

The register file contains twelve 64-bit data registers, a 32-bit status register, and seven 32-bit registers for reporting exceptional conditions, as shown in Fig. 1. The twelve data registers also form six 128-bit quad-precision registers. The data registers are numbered from 4 through 15. Register 0 holds the status register. When register zero is used as the target or source of a coprocessor load or store, the status register is referenced. But when used as the source of an operation, register zero returns a floating-point zero. This is used for simple assignments, arithmetic negation, and comparisons with zero.

The status register holds information on the current rounding mode, the exception flags, and exception trap enables for the five IEEE exceptions: overflow, underflow, divide by zero, invalid operation, and inexact. If the exception trap is not enabled, then a default result is returned and the corresponding exception flag is set in the status register. If the exception trap is enabled, an interruption to the main processor occurs, with the exception and the instruction causing it recorded in an exception register. On overflow, underflow, and inexact exceptions, the correctly rounded result is delivered to the destination register. On invalid operation and divide-by-zero exceptions, the source registers are preserved. Users can specify a trap handler for any of the five IEEE exceptions, using the information preserved.

The coprocessor uses an additional nonmaskable exception, called unimplemented, to pass off to software those operations not implemented by the coprocessor hardware. The unimplemented trap triggers a software emulation of the desired operation with the original operands.

The Boolean result of a floating-point comparison is stored in a bit in the status word. This bit can conditionally nullify the next instruction when tested. No conditional branch is allowed. A conditional branch would have increased the critical path for branch determination.

#### **Floating-Point Operations**

The floating-point coprocessor defines eleven fundamental operations in three precisions. All of the operations, except for conversions to fixed-point formats, produce floating-point results. Source and destination formats are the same except for conversions that have explicit source and destination formats. Rounding is specified by a mode field in the status register. The COPY and ABSOLUTE VALUE operations are nonarithmetic and do not cause exceptions. The following table summarizes the defined arithmetic operations for single, double, and guad formats.

| FADD  | Addition       |

|-------|----------------|

| FSUB  | Subtraction    |

| FMPY  | Multiplication |

| FDIV  | Division       |

| FREM  | Remainder      |

| FSQRT | Square Root    |

| FRND  | Round          |

| FCMP  | Compare        |

CONVERSION instructions from floating-point formats to fixedpoint formats and between floating-point formats are also included. When converting from floating-point to fixed-point format, the current rounding mode can be temporarily changed to roundto-zero. Many programming languages define conversion to integer as rounding to zero. In accordance with the standard, the default rounding mode is rounding to the nearest integer.

#### Scalability and Performance

HP Precision Architecture is designed to adhere strictly to the IEEE floating-point standard. The standard does not, however, require that all floating-point operations be performed in high-performance hardware, and does not specify the instruction set level presentation of the hardware. Whenever there is little performance advantage to be gained by performing an operation in hardware, consideration should be given to simplifying the hardware and performing the operation in software. The unimplemented exception trap mechanism is employed to avoid handing operations and exceptional conditions in hardware.

The simplest HP Precision systems may completely exclude a floating-point unit. Each floating-point instruction causes an assist emulation trap and system software completely simulates the function. Special control registers speed the simulation of load and store instructions. Some implementations can reduce the complexity of hardware control by supporting only those operations that use available floating-point hardware. In this case, exceptional conditions arise that can require additional processing or software assistance. For example, the unimplemented exception trap mechanism can be used to handle the square root operation and corner case operands like infinities, NaNs (not a number), and denormalized numbers.

The floating-point coprocessor is architected to be pipelined to allow very high-performance numeric processing. Fundamental to this is the delaying of exception reporting. If the coprocessor must inform the basic processor immediately that the current instruction overflows, then little concurrent processing and pipelining is possible. In HP Precision Architecture, the coprocessor can freely accept a non-load/store operation independent of any

lows the specification of premodification or postmodification without using up a bit of the long displacement field. Memory accesses with long displacement fields perform predecrement or postincrement, depending on the sign of their displacements. In theory, this is less general than allowing the specification of premodification or postmodification to be orthogonal to the sign of the displacement, as is true for the short-displacement load and store instructions. In practice, however, the feature works very well for maintaining stacks stored in the memory. For example, for a stack growing in the direction of decreasing memory addresses, pushing onto the stack from a register is done by a store with predecrement and popping off the stack is done by a load with postincrement.

#### Combined Instructions

The basic types of operations in most instruction sets fall into three categories: data transformation operations, data movement operations, and control operations. In general, one instruction performs one of these operations. A *combined instruction* performs more than one of these operations in one instruction. In HP Precision Architecture, almost every instruction performs a combination of two of these operations in a single cycle, with relatively simple hardware.

HP Precision Architecture has two types of data transformation and control operation combinations. The first type has a more general transformation operation combined with a restricted control operation, whereas the reverse is true for the second type. Examples of the first type are ADD instructions that can conditionally skip the execution of the following instruction. Examples of the second type are COMPARE AND BRANCH instructions.

The LOAD and STORE instructions combine a data movement operation (moving data between a general register and the memory system) with a transformation operation (the accompanying address calculation and modification).

HP Precision Architecture's combined instructions allow the execution engine to be used efficiently, since the data earlier operations, provided space exists in the exception registers to report exceptions. This allows seven instructions to be in execution simultaneously while the basic processor continues. Load and store instructions to independent data registers can also be fully overlapped. The coprocessor need only complete pipelined instructions when the result is being requested. References to the status register are special and require all operations to be completed.

A minimally pipelined machine might perform only a single floating-point operation at a time, but permit load and store operations to execute concurrently. This requires an interlock against stores of the single result register specified in the executing operation, and an interlock on the source registers during the period that the source exceptions are tested in the operations. The second interlock may never occur in some implementations.

The floating-point instruction set is designed to allow software the option of performing pipelined operations without the need for complex hardware control. The high-level language optimizer places instructions in a sequence to avoid the most common interlocks. The use of results is delayed as long as possible and effective overlap with other integer operations is obtained.

transformation portion of a combined instruction is performed in the simple execution engine shown in Fig. 3.

#### Assist Instructions

The architecture allows for flexible instruction set extensions by means of assist instructions. Assist instructions are instructions in which the data movement functions are defined between the processor or the memory and the assist hardware, but the data transformation functions are left unspecified. An extension instruction is defined by specifying in an assist instruction the data transformation operations to be performed by the assist hardware. Assist hardware is optional hardware that accelerates the execution of a set of assist instructions. In the absence of the assist hardware, an extension instruction is emulated by software, using a transparent assist emulation trap mechanism. Critical information required for emulation is saved in control registers, substantially reducing the emulation time.

HP Precision Architecture allows up to sixteen assists in a system configuration, supporting sixteen logically differentiated sets of instruction set extensions. These are divided into two generic types of assists: the special function units (SFUs) and the coprocessors (COPs).

Special function units use the general registers as sources and targets of operations. They are coupled very closely to the basic processor and its register buses.

Coprocessors provide functions that use either memory locations or coprocessor registers as operands and targets of operations. They are coupled less closely to the basic processor. Coprocessors may also directly pass doubleword quantities between the coprocessor and the memory. This is suited to the manipulation of quantities that are too large to be handled directly in the general registers.

The HP Precision instruction set can be extended by defining a set of assist instructions in applications where specialized hardware is justified by its frequency of use or by the resulting performance improvement. The architecture allows such instruction set extensions without compromising software compatibility. An example of such an instruction set extension is the instruction set for the floating-point coprocessor (see box, page 8).

#### **Control Flow Model**

HP Precision Architecture defines a computer in which the flow of control passes to the next sequential instruction in the memory unless directed otherwise by branch instructions, nullification of instructions, or interruptions. These three mechanisms can potentially alter the sequential flow of control in instruction processing.

#### Branching

The architecture has both unconditional and conditional branch instructions. All branch instructions exhibit the delayed branch feature.

In a pipelined processor, it is difficult to execute a branch instruction in one cycle, since the branch target address has to be calculated before the target instruction can be fetched. Hence, taken branches frequently result in pipeline interlocks, in the absence of other prefetch mechanisms.

To minimize such pipeline interlocks, HP Precision Architecture defines a one-instruction delayed branch. This means that a *delay instruction*, which is the instruction following a branch instruction, is executed before the program control flow passes to the target instruction of the branch. The delay instruction is not executed when it is explicitly nullified by its preceding branch instruction. This branch nullification feature is explained later.

The delayed branch mechanism allows compilers to schedule a useful instruction in the cycle during which the branch target address is calculated. For example, this might be an instruction that preceded the branch instruction.

**Unconditional Branching.** HP Precision Architecture defines *local* branches, where the control flow passes to another location within the current virtual space and external branches, where instruction processing continues at a location that may be in a different virtual space.

The design of high-speed pipelines is simplified if branch target address calculations can be made before the execution of the branch instruction itself. In HP Precision Architecture, the most common branch instructions have branch targets calculated relative to the address of the branch instruction itself, with displacements given in the branch instruction. These are called *relative* branches with *static displacements*, Unconditional branch instructions have a 17-bit signed displacement field, and the conditional branches have a 12-bit signed displacement field.

Although a 17-bit displacement will cover almost all branch distances, it is insufficient in certain situations. Furthermore, it is not always possible or convenient to generate a static displacement at compile time for some branches. Hence, the architecture includes branch instructions with 32-bit dynamic displacements specified by the contents of a general register.

Branches are also needed to locations that have no relation to the address of the branch instruction—for example, to independent relocatable modules. This is called *absolute* branching, since the address of the target instruction can be anywhere in the address space. HP Precision Architecture also allows absolute branches: the branch displacement is added to the contents of a general register called the base register.

**Subroutine Calls.** The subroutine call primitives are BRANCH AND LINK instructions, which save the return address of the calling routine in a general register before transferring the control flow to the subroutine. Both local (intraspace) and external (interspace) subroutine calls are defined. The external subroutine calls must save a larger return pointer, indicating also the virtual space of the caller.

The external BRANCH AND LINK instruction uses implicit link registers for saving both the caller's space identifier and the offset within that space. Space register zero (SR 0) is used for saving the space identifier and general register thirty-one (GR 31) is used for saving the offset address. This permits the maximum number of bits to be used for encoding the static branch displacement.

Subroutine returns are accomplished by using an absolute branch instruction, specifying the general register used to save the link address in the BRANCH AND LINK calling instruction. If appropriate software conventions are used, a uniform subroutine return sequence can be used for both local and external calls.

**Inter-Ring Branches.** Four hierarchical protection rings are implemented in HP Precision Architecture. Each ring has a privilege level associated with it, the innermost ring (privilege level 0) being the most privileged ring and the outermost ring (privilege level 3) being the least privileged ring.

The architecture defines unconditional branch instructions that perform inter-ring crossings in one instruction. Three of these are outward branches, causing a decrease in the process privilege level. Only one branch instruction (GATEWAY) is an inward branch, causing an increase in privilege level.

**Conditional Branching.** In many architectures, conditional branching is accomplished by two separate instructions. The first instruction calculates a condition, and saves the result of this condition calculation in state flip-flops in the processor called a *condition code*. A subsequent conditional branch instruction may alter the program's control flow depending on the value of the condition code.

Statistics of instruction sequences show that in an overwhelming majority of cases, a conditional branch instruction is immediately preceded by the instruction that sets the condition tested by the branch. HP Precision Architecture capitalizes on that fact by combining the two instructions into one instruction, thus achieving code compaction, reduction of execution time, and elimination of condition code flip-flops in the processor state. Each conditional branch instruction includes a data transformation operation, which generates a condition that is used immediately to determine whether the branch is taken or not. Such conditional branch instructions also provide greater opportunities for an optimizer to reorder instructions, with less bookkeeping.

There are four kinds of operations that can be executed with a conditional branch instruction. The ADD AND BRANCH instruction is useful for closing loops. The COMPARE AND BRANCH instruction is useful for closing loops and for ifthen-else control structures. The BRANCH ON BIT instruction allows branching on the value of any bit in a general register. The MOVE AND BRANCH instruction is useful for reinitializing a register before branching away.

HP Precision Architecture also implements a special nullification scheme to optimize the use of the delay instruction following a conditional branch instruction.

#### Nullification

HP Precision Architecture defines a control flow feature called the nullification of the immediately following instruction. When an instruction is nullified, it executes as a no-operation (NOP), and the effect is as if it had never been in the instruction stream. This means that no change in any architecturally visible state, like general registers, memory, control registers, or space registers occurs because of a nullified instruction. A nullified instruction does not cause any traps to be generated, and it does not cause its successor instruction to be nullified. All branch instructions and data transformation instructions have the ability to nullify the instruction to be executed next.

All branch instructions have a single-bit nullification field. An unconditional branch instruction can "always nullify" or "never nullify" the execution of its delay instruction by setting the value of the nullification field to one or zero, respectively. A conditional branch instruction can "conditionally nullify" or "never nullify" the execution of its delay instruction in the same manner. The never nullify feature is used whenever a delay instruction can be found that can always be executed, regardless of whether the branch is taken or not.

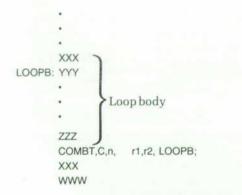

A conditional branch is taken when the condition it specifies evaluates true. To optimize the use of the delay instruction following the conditional branch, the delay instruction is nullified for backward branches only if the condition is false, and for forward branches only if the condition is true. Since the compilers use the convention that loops are closed with backward branches, the delay instruction of this branch can now be "inside" the loop, saving a cycle on each iteration. The following example illustrates this.

As shown, the first instruction (XXX) of the loop body can always be duplicated following the loop-closing branch, COMBT. When the COMBT instruction is executed, if condition C is true, then the XXX instruction is executed and control passes back to LOOPB. Otherwise, the next instruction (XXX) is nullified and processing continues with instruction WWW.

For forward branches, the nullification definition allows shorter code sequences for if-then constructs, as shown in the following example.

When the conditional branch instruction, COMBT, is executed, if condition C is true, the next instruction is nullified and the branch is taken around the "Then" code to the location THRU. Otherwise, the next instruction (TTT) is executed.

Every data transformation instruction has an implicit conditional skip operation built into it. In a single cycle, the function specified by the transformation instruction is performed by the execution engine, and a condition specified in the instruction is evaluated. If the condition evaluates true, then the next instruction to be executed is nullified. If the condition evaluates false, then the next instruction is executed, or not nullified.

The following example shows the use of nullification in an ALU instruction to implement a compact control sequence for a high-level language construct.

High-level language: if (a < b) then b = b + 1;

Equivalent HP Precision assembly language:

| SUB,>= | a,b,r0; | Subtract [GR b] from [GR a], discarding the result, and nullify next instruction if          |

|--------|---------|----------------------------------------------------------------------------------------------|

| ADDI   | 1,b,b;  | [GR a] ≥ [GR b].<br>Add the immediate value 1 to [GR b],<br>writing the result back to GR b. |

**Conditional Trap.** In some instructions, the condition specified in the instruction is used to cause a conditional trap, rather than the nullification of the next instruction. An advantage of taking a conditional trap rather than conditionally nullifying a branch to a trap routine is that the majority of instructions do not incur the penalty of a nullified instruction. For example, when an add or subtract instruction is used to perform range checking, the penalty of a conditional trap is taken only in the rare cases where the range check fails. While it is a common feature of other architectures to have an ALU instruction trap on arithmetic error conditions like overflow, it is a special feature of HP Precision Architecture to allow trapping on defined conditions that are not arithmetic errors.

Assist Nullification. In assist nullification, the condition upon which nullification is performed is generated by the assist hardware rather than by the basic processor. Instead of defining assist branch instructions, the processor's unconditional branch instructions are used for control flow changes in assist programs. The equivalent of conditional branching is achieved using a pair of instructions: a data transformation assist instruction with its nullification field set to one, followed by an unconditional branch instruction. The assist instruction generates a condition that determines whether the following branch instruction should be nullified.

An assist can be defined with the nullification operation dependent upon the condition generated either in the current assist instruction or in the previous assist instruction. The latter is called *delayed nullification*. Delayed nullification allows other instructions, executed by the basic processor or other assists, to be scheduled during the time the assist hardware is performing a lengthy computation that generates the condition for determining nullification.

#### Interruptions

Interruptions are anomalies that occur during instruction processing, causing the control flow to be passed to an interruption handling routine. In the process, certain processor state saves and changes are made automatically by the hardware. Upon completion of interruption processing, a RETURN FROM INTERRUPT instruction is executed, which restores the saved processor state, and execution proceeds with the interrupted instruction.

Traps, faults, checks, and interrupts are different anomalies that may happen during instruction processing on a computer. In HP Precision Architecture, they are all handled by the same basic mechanism. The term interruptions is used in discussing these anomalies as a group.

The architecture implements a *single-level* interruption system. This means that once an interruption is chosen for service, it cannot be preempted for service by a higherpriority interruption. It also implies that only one interruption is serviced at a time. If an instruction raises multiple interruptions, the highest-priority interruption is serviced, and then the instruction is reexecuted, which causes the other interruptions to be raised again. Then the next highest-priority interruption is serviced, and so on.

The nesting of interruptions is not excluded, since the interruption handling routine can choose to reenable other interruptions once it has saved the appropriate state. Since the machine state is saved in registers rather than in memory when an interruption is serviced, interruption handlers must leave interruptions disabled until they have saved the machine state in memory.

In certain pipelined processors, interruptions are often not precise, in the sense that they may not be serviced immediately after the instruction that caused the interruption. This is because in overlapped instruction processing, several successive instructions may already have been partially or fully processed by the time the interruption caused by an instruction is generated. This imprecision adds considerable complexity to interrupt handling routines.

In a nonoverlapped processor, precise interruptions are easy to implement, since an instruction is fetched and completely executed before the next instruction is fetched. Hence, interruptions can be serviced between instructions, that is, after the instruction causing the interruption and before the next instruction's processing starts.

HP Precision Architecture requires that interruption servicing appear the same for both overlapped and nonoverlapped processors. Hence, all implementations must provide precise interruptions, and resume execution at the same instruction as a nonoverlapped implementation.

**Traps and Faults.** Traps and faults are synchronous interruptions, meaning that they are caused by the processing of an instruction or a sequence of instructions. A *trap* occurs when the function requested by the current instruction cannot or should not be carried out, or system intervention is desired by the user before or after the instruction is executed. A *fault* occurs when the current instruction requests a legitimate action that cannot be carried out because of a system problem, such as the absence of a page from main memory. After the system problem has been corrected the faulting instruction will execute normally.

In HP Precision Architecture, the overflow trap and the conditional trap occur for arithmetic instructions. The privileged operation or privileged register traps occur when certain system management instructions or control registers are accessed by a process with insufficient privilege. An illegal instruction trap is generated for undefined operation codes, or illegal instruction sequences which could otherwise cause security breaches. The assist exception and emulation traps allow assist hardware to request the processor to service assist-generated traps, or to emulate assist instructions not supported by hardware.

Virtual memory faults and traps may also be generated for instruction fetches or data fetches in virtual mode. For example, if the virtual-to-physical address translation is not found in the hardware translation lookaside buffer, a TLB miss fault is generated. If a virtual memory access fails the protection checking required for the access, then a memory protection trap is generated. These traps are generated independently for instruction and data virtual accesses. The first time a page is written, a TLB dirty-bit trap occurs, which is used by the system to distinguish unmodified pages from modified (dirty) pages at page replacement time.

HP Precision Architecture also has a rich set of debugging support traps. A BREAK instruction is defined in the architecture to allow the insertion of software breakpoints. Whenever such an instruction is executed, a break trap occurs. Any store instruction to a virtual address may also generate a data memory break trap, if this trap is enabled by a bit in the TLB entry. This allows the tracing of all data updates to a given page. A similar facility traps on any reference whatsoever to a given virtual page. Traps may also be generated, if enabled, after a branch is taken, or when the privilege level of the running process is promoted or demoted. Architectural support for software rollback schemes is also implemented by means of a recovery counter trap. A 32-bit control register, the recovery counter, can be initialized to any integer value. If enabled, the counter is decremented for every nonnullified instruction that is executed, and a recovery counter trap is generated when a zero value is reached. The recovery counter can be used in fault recovery, to permit an exact reexecution of the instruction stream since the last checkpoint.

Checks and Interrupts. A check occurs when a hardware malfunction is detected. Depending on the nature of the malfunction, checks may be synchronous or asynchronous with respect to the instruction stream. HP Precision Architecture defines two types of machine checks: a highpriority machine check and a low-priority machine check.

An interrupt occurs when an external entity, like an I/O device or the power supply, requires attention. Interrupts are asynchronous with respect to the instruction stream.

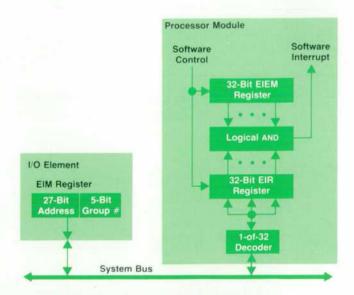

There are thirty-two external interrupt classes, each of which can be individually masked by privileged software. The architecture defines two control registers specifically for handling these external interrupts. The external interrupt request (EIR) register and the external interrupt enable mask (EIEM) register each have thirty-two bits, one for each external interrupt class. A privileged instruction allows the writing of any set of mask bits to the EIEM register and the clearing of any selected bits in the EIR register. When an external interrupt of any class occurs, its corresponding interrupt pending bit is set in the EIR register. If the corresponding mask bit in the EIEM register is also one, then an external interrupt is taken. An EIR register bit remains set, leaving the external interrupt pending, until explicitly reset by an interruption handler.

Relative priority of these thirty-two external interrupt classes is not assigned by the architecture or by the hardware. When multiple unmasked external interrupts occur simultaneously, or when there are multiple external interrupts pending in the EIR register, the external interrupt handler selects the order of service.

**Interruption Parameters and Servicing.** Six control registers are defined to save interruption parameters and expedite the processing of interruptions. The collection of information in these interruption parameter registers occurs only when the interruption state collection enable flag (Q bit) in the processor status word (PSW) is set.

These interruption parameter registers save the processor status word of the interrupted process, the instruction that is interrupted, and the data address (space and offset portions) for memory reference instructions. Two other register pairs form two queues, saving the space and offset portions of the addresses of the first two instructions to be processed upon returning from the interruption.

The two queues are necessary because in an architecture with delayed branching, at least two return addresses must be saved before jumping to the interruption handler. Two are necessary because the last instruction to be completed before the interruption may be a taken branch. In this case the next two instructions to be executed may not be contiguous, since one is the delay instruction and the other is the target instruction. These queues are constantly updated by the hardware whenever interruption parameter collection is enabled. When an interruption is taken, the queues and other interruption parameters are preserved by disabling further interruption collection.

Interruption servicing is implemented as a fast context switch, which is much simpler than a complete process swap. When an interruption occurs, the current processor status, represented by the PSW, is saved. Then, the PSW is cleared to zeros to disable further interruptions, to enable real-mode addressing, and to freeze the information collected in the interruption parameter registers. The current privilege level is set to the highest privilege level. The control flow then passes to a vectored location in an interrupt vector table, which is dynamically relocatable. This simple set of architecturally defined operations facilitates a fast and uniform switch to interruption servicing for all implementations.

#### **Addressing and Protection Model**

HP Precision processors access memory using byte addresses. Larger addressable units include half words, words, and double words. An address is either physical or virtual. All load and store instructions can be used in either virtual or physical mode. Virtual mode is enabled separately for instruction fetches and data accesses by two flags in the processor status word.

A pointer to physical memory is a 32-bit unsigned integer whose value is the address of the first byte of the operand it designates. Physical addresses are used directly, with no protection or access rights checking performed. Virtual addresses are translated to physical addresses and undergo protection and access rights checking as part of the translation. This allows the hardware support for access control to be built into the storage unit.

The input/output (I/O) architecture is memory mapped. That is, complete control of all system components (of which I/O attachments are a special case) is exercised by the execution of load and store instructions to virtual or physical addresses. This approach permits I/O drivers to be written in high-level languages. Furthermore, since the usual page-level protection mechanism is applied during virtual-to-physical address translation, user programs can be granted direct control over particular I/O devices without compromising system integrity.

#### Virtual Memory Addressing

A virtual address is defined globally and has the same meaning when used by any process. This is in contrast to other architectures, which permit use of the same address for different objects by different processes. The virtual address space is so large that processes can be assigned separate address ranges for private data. Address translation information does not need to change upon a process switch and the information needed for address translation can be represented more compactly. Global virtual addressing therefore allows closely coupled processes to accumulate a stable working set of address translations in spite of frequent process switching.

Virtual memory is structured as a set of address spaces, each containing 2<sup>32</sup> bytes. A level-one processor implements 2<sup>16</sup> spaces (16-bit space registers), and a level-two processor implements 2<sup>32</sup> spaces (32-bit space registers). A space is specified by a space identifier, and is divided into pages, each 2048 bytes in length.

For a level-two processor, the concatenation of a 32-bit space identifier and a 32-bit offset within the space forms a virtual address. Alternatively, a virtual address may be viewed as the concatenation of a 53-bit virtual page number and an 11-bit offset within the page.

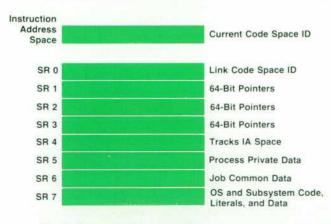

For virtual addressing, space identifiers are specified in space addressing registers. These include the space portion of the instruction address register and the eight space registers SR 0 through SR 7 (see Fig. 4). One such register is implicitly or explicitly selected by every instruction that generates a virtual address.

SR 0 is used as an implied target by the interspace procedure call instruction. SR 1 through SR 7 have no architecturally defined functions, but it is expected that their use will be constrained by the following software conventions. SR 1 through SR 3 are used as scratch registers for the manipulation of 64-bit virtual pointers. SR 4 tracks the current program's space and provides access to literal data contained in the current code space. SR 5 points to a space containing process private data, SR 6 to a space containing data shared by a group of processes, and SR 7 to a space containing the operating system's code, literals, and data. The conventions for SR 4 through SR 7 were chosen to permit use of 32-bit virtual address pointers (see below) for almost all data references.

SR 5 through SR 7 can be modified only by code executing at the most privileged level. SR 0 through SR 4 can be changed by an unprivileged user. Shared libraries or subsystems will be assigned individual code spaces, and branching into those other spaces will involve changing SR 4.

**Instruction and Data Addressing.** Instruction addresses are computed for instruction fetch, instruction cache flush instructions, instruction TLB instructions, and branch target calculations. Instructions that explicitly reference a space register use the 3-bit S field, located in the instruction, to designate one of the eight space registers.

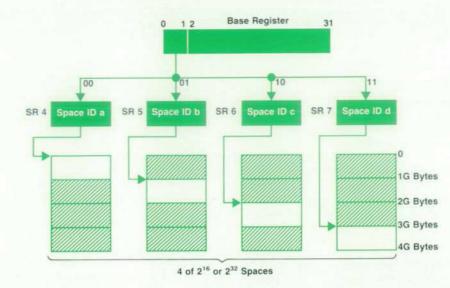

Data addresses are computed for load, store, semaphore, probe, data cache, and data TLB instructions. Data addresses specify one of the eight space registers in an interesting way: only a 2-bit S field in the instruction is used. When the 2-bit S field is nonzero, it selects the corresponding

Fig. 4. Space register conventions.

space registers 1, 2, or 3. When the S field is zero, the space register is designated by adding four to the two high-order bits of the base register specified in the instruction. This allows the selection of space registers 4 through 7.

Data references with the S field equal to zero allow addressing of four distinct spaces selected by the high-order bits of a 32-bit pointer. This is called *short-pointer* addressing (Fig. 5), since a 32-bit value both specifies an offset and selects a space register. Only one fourth of each space is directly addressable with short pointers. This region corresponds to the quadrant selected by the upper two bits. For example, if a base register contains the hex value 80001000, the content of space register 6 is the space identifier and the third quadrant of the space is directly addressable.

Short-pointer addressing allows the pointer data type of conventional languages to be 32 bits in length. Therefore, such pointers can be handled efficiently in the general-purpose registers. Also, pointers are the same length as the standard integer data type, a situation assumed by a number of existing high-level language programs. Long pointers are 48 bits or 64 bits in length, consisting of a 16-bit or 32-bit space identifier together with a 32-bit byte offset within the space, for level-one and level-two processors, respectively.

#### Software Virtual Address Translation

TLBs (see box, page 16) do not contain the translations for all pages in memory simultaneously. When they do not have the desired translation, a TLB miss occurs. In many architectures, TLB misses are handled in microcode. In HP Precision Architecture, they may be handled in software. When a TLB miss is detected, the hardware does not have sufficient information to complete the instruction being executed. Instead, an interruption is generated to invoke the appropriate TLB miss handler. One miss handler handles misses during instruction fetch, and another handles misses during data access. The virtual address causing the miss is directly available to the TLB miss handler in interruption parameter control registers to expedite miss handling.

Because of the critical effect on system performance of the speed of address translation, all information required to translate the virtual address of a page that is actually present in physical memory must be permanently resident in memory. Because of the size of the virtual address space, tables describing all virtual pages cannot be kept permanently in memory. Thus the data structures used to translate valid virtual addresses (no page fault) describe only physically present pages and have a size proportional to the size of physical memory, consuming less than 2% of the available memory. The information represents a one-toone mapping between physical and virtual pages. Thus it cannot support memory aliasing (see box, page 16) or process-specific address translation. A desire to use these efficient structures was an important motivation for disallowing both features.

This address translation information resides in a physical page directory (PDIR). The physical-to-virtual address translation is obtained by using the physical address as a direct index into the PDIR. The translation of a virtual address to a physical address is accomplished using two tables, the hash table and the PDIR. Each table is located

Fig. 5. Short-pointer space selection allows addressing of four distinct spaces selected by program data.

by a pointer which defines its absolute starting address. For efficiency, these pointers are kept in control registers (assumed to be CR 24 for the PDIR address and CR 25 for the hash table address).

The purpose of the hash algorithm is to map virtual addresses to a smaller, denser name space. The number of entries in the hash table is typically a multiple of the number of entries in the PDIR, rounded up to the nearest power of two. Since multiple virtual addresses can map into the same hash table entry, they are linked together as a chain of PDIR entries. The TLB miss handler hashes the virtual address, looks up the start of the chain in the hash table, and looks through the chain in the PDIR until it finds either the match or the end of the chain. If it finds the match, it puts the information from the PDIR into the TLB and retries the instruction. If it finds the end of the chain, the page is not in memory and a page fault is signaled by the software.

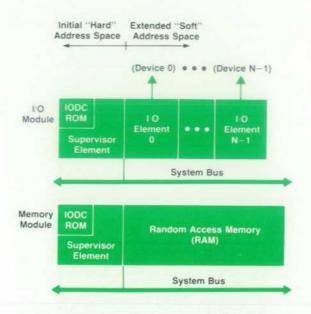

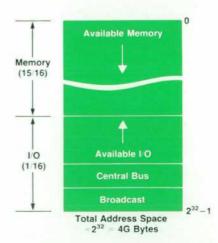

The physical page directory (PDIR) contains one entry for each page of physical memory, plus one for each physical or virtual I/O device. The entries for physical pages are at nonnegative offsets from the location pointed to by CR 24, and the I/O entries are at negative offsets. This arrangement corresponds to the layout of the 32-bit physical address space which places physical memory at the lower end of the space and memory mapped I/O devices at the upper end.

The design of the hash table and PDIR are such that later implementations can service TLB misses in hardware, with a reduction in the time spent servicing TLB misses. Control registers have been reserved to contain the hash table address and PDIR address.

**Paging Management.** One function of an operating system is to swap out pages that have not been accessed recently, to make room for pages being accessed that are still on disc. To help implement this, there is a reference bit for each page, within the PDIR entry, even though there is no hardware bit corresponding to it in the TLB. Instead, the entry is only allowed to be in the TLB if the reference bit is set. When the reference bit is cleared, the TLB entry is also purged by software. The next time there is a TLB miss, the miss handler will also set the reference bit in the PDIR. Thus, the operating system can clear the reference bit, and if the bit is still clear sometime later when it examines it again, it knows that the page has not been accessed in the meantime.

Each entry of the PDIR (and the TLB) has a dirty bit that tells whether the page has been modified since it was brought in from disc. When the page is first brought in, the dirty bit is clear. As long as only reads are done to the page, the bit will remain clear. However, the first time a program tries to store data to that page, the TLB causes a dirty bit update trap, which sets the bit to one in both the PDIR and the TLB. This provides information to the operating system so that it can avoid writing out unmodified pages, since the copy on disc is still valid.

#### Access Control

Access rights checking is based on the access rights and access ID fields in the TLB entry used to perform the translation. Access rights checking occurs with virtual address translation, unless disabled by the P flag in the PSW. There is no access control when using physical addressing.

Fields in the TLB entry for a particular page permit control of access to the page in three dimensions:

- Which of data read, data write, instruction execute, and the privilege level change function of the GATEWAY instruction are permitted (What)

- The privilege level at which the process must be executing (When)

- The process or group of processes allowed to access the page (Who).

These three dimensions are provided by two independent, simple mechanisms that combine to provide the required protection which can be evaluated in parallel to provide efficient access control. The combination is designed to support both conventional and virtual machine operating systems.

Access Rights. The first two dimensions of access control are provided using the access rights field of the TLB entry and the process privilege level. There are four levels (0 to 3), with 0 being the most privileged. Associated with each

#### **HP** Precision Architecture Caches and TLBs

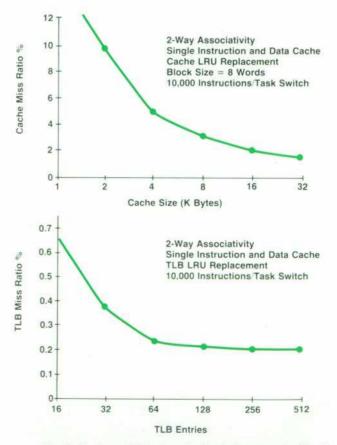

An HP Precision processor typically interfaces to the memory system via the translation lookaside buffer (TLB) and the cache memory. The architecture is designed to allow simple, highspeed implementations by making the TLB and cache visible to software, and by placing constraints on software. The architecture also explicitly separates instruction and data caches, and instruction and data TLBs, although this is not a restriction on hardware implementations.

A cache is a small, high-speed memory that shortens main memory access times by keeping copies of the most recently accessed data. The cache is divided into blocks of data, and each block has an address tag that specifies the corresponding block of memory. When the processor accesses data, the block is copied from main memory into the cache. If the processor modifies the data (by doing stores), the copy in the cache will be more up-to-date than the copy in memory. The stale data in the memory at the place specified by the tag is eventually updated to correspond to the new data in the cache, using either the copy-back or the write-through update strategies.

Similarly, a *TLB* speeds up virtual address translations by acting as a cache for recent translations. When the processor accesses memory with a virtual address, the TLB checks for an entry with that virtual page number. If it is present, the corresponding physical page number is used to generate the physical address. Otherwise, there is a TLB miss, which must be serviced before the virtual memory access can be finished.

To allow the implementation of large, high-speed caches, the architecture disallows *address aliasing*, the capability of having two different virtual pages mapped to the same physical page. While address aliasing is of some use to software, it has severe impact on cache design. Normally, a portion of the address

process is a current privilege level.

The access rights information is encoded in seven bits divided into three fields: type, first privilege level (PL1), and second privilege level (PL2) fields. The type field defines the use of the page (data or code) and, for privilege promotion instructions, the privilege level to which the process will be promoted. PL1 and PL2 define the privilege levels required for read, write, or execute access to the page. The meaning of the type field and the interpretation of PL1 and PL2 are given in Fig. 6. Read and write fields specify the least privileged levels allowed to read or write the page, respectively. Xleast gives the least privileged level allowed to execute instructions from that page. Xmost gives the most privileged level allowed to execute instructions from the page and is used to prevent privileged code from inadvertently branching onto a page that cannot be trusted.

The privilege level mechanism allows a process to have different access rights over time without the overhead of changing TLB entries when access changes or at process switch. Thus user programs (privilege level 3) can invoke the services of an operating system supervisor (privilege level 1) or kernel (privilege level 0) using an efficient procedure call and no interruption or process switch is required.

The entry to a more privileged routine can be implemented as a procedure call to a GATEWAY instruction that branches to the body of the routine. If a GATEWAY instruction is fetched from a proprietary code page, then when it executes it changes the privilege level to that called the index is used to specify a block or a small group of blocks to be examined for a matching tag, instead of examining all blocks in the cache. Address aliasing precludes using the virtual page as part of the index. Otherwise, a virtual access could put data into the cache based on its index, and a later virtual access, using the other (aliased) address, would not find it in the cache because the index was different in the virtual page portion. The second access would then go to main memory, where it would get an inconsistent or stale copy.

Since HP Precision Architecture prohibits the use of address aliasing, the cache can use the virtual page portion of the address as part of the index, without causing the stale data problem described above. This allows the cache to be accessed in parallel with the TLB without restricting the size of the cache to that of the page size multiplied by the set-associativity of the cache organization.

If an object is to be referenced by both its virtual address and its corresponding physical address, software must flush the cache before accessing the data in the other mode. The one exception is if the physical and virtual addresses are identical, namely, the virtual address is in space zero and the offset within the space is the same as the physical address. Since the addresses are identical, the index chosen by the cache would be identical, thus avoiding the above stale data problem. This case is called equivalent mapping.

#### **Uniprocessor Cache Management**

HP Precision Architecture makes caches visible to software, and supports separate instruction and data caches when desirable for extra bandwidth, or a unified cache for reduced expense. It will also support very low-cost systems without caches, where

specified by the low-order two bits of the type field for that page (if that level is more privileged than the current level). The GATEWAY instruction stores the caller's privilege level in the return address register so that it cannot be "forged" by the caller.

The architecture defines two trap conditions (higher and lower privilege transfer traps) that can be enabled to allow an operating system to intercept privilege level changes. These are provided to support languages that allow multiple processes to share a single stack with different access rights.

Access ID. A second field in the TLB entry, the 15-bit access ID, provides the third dimension of access control. It allows each process sharing memory to access different domains in memory without the overhead of changing fields in the TLB (and associated data in memory) on process switch.

|      | Type (3)    | PL1 (2) P  | L2 (2)                |

|------|-------------|------------|-----------------------|

| Туре | PL1         | PL2        | Use                   |

| 0    | Read        | -          | Read-Only Data Page   |

| 1    | Read        | Write      | Normal Data Page      |

| 2    | Read/Xleast | Xmost      | Normal Code Page      |

| 3    | Read/Xleast | Write/Xmos | st Dynamic Code Page  |

| 4-7  | Xleast      | Xmost      | Proprietary Code Page |

Fig. 6. Interpretation of access rights fields.

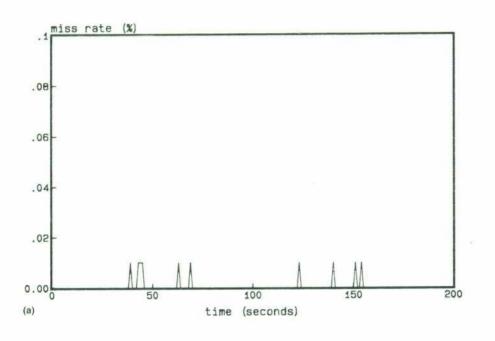

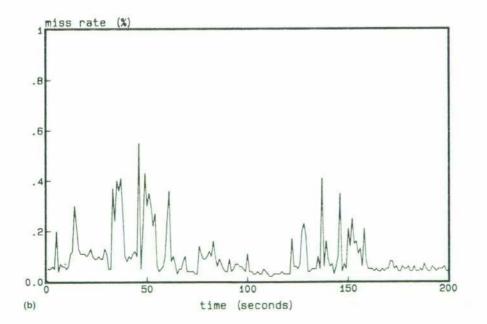

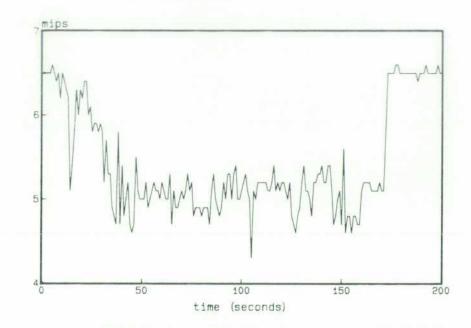

the cache control instructions are treated as NOPs.